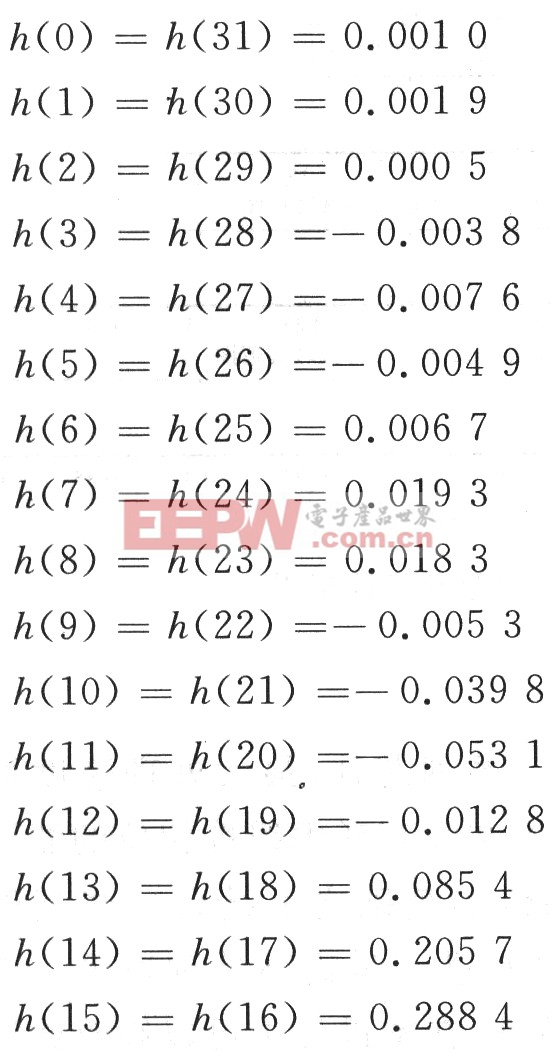

采用上面介紹的凱澤窗�����,利用Matlab編程計算得到32階FIR低通濾波器參數如下:本文引用地址:http://www.butianyuan.cn/article/188447.htm

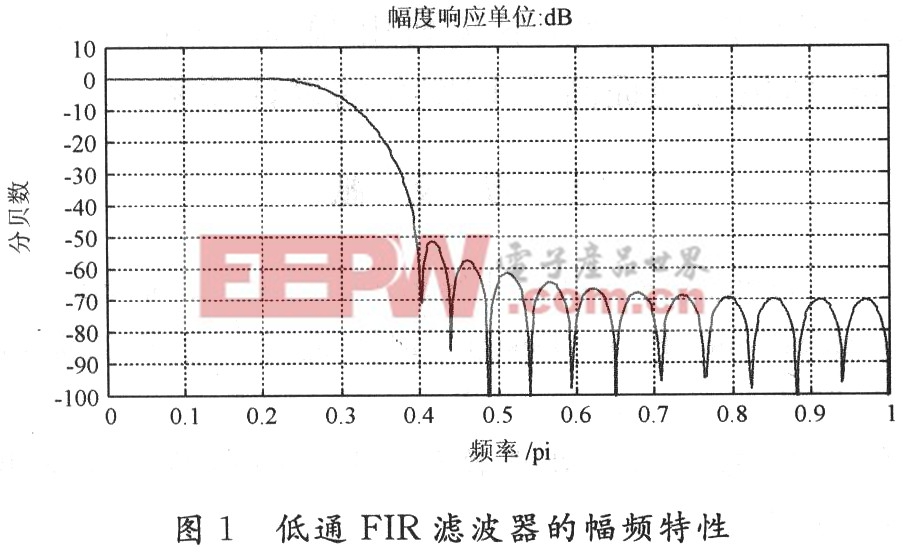

32階FIR低通濾波器幅頻特性圖如圖1所示。

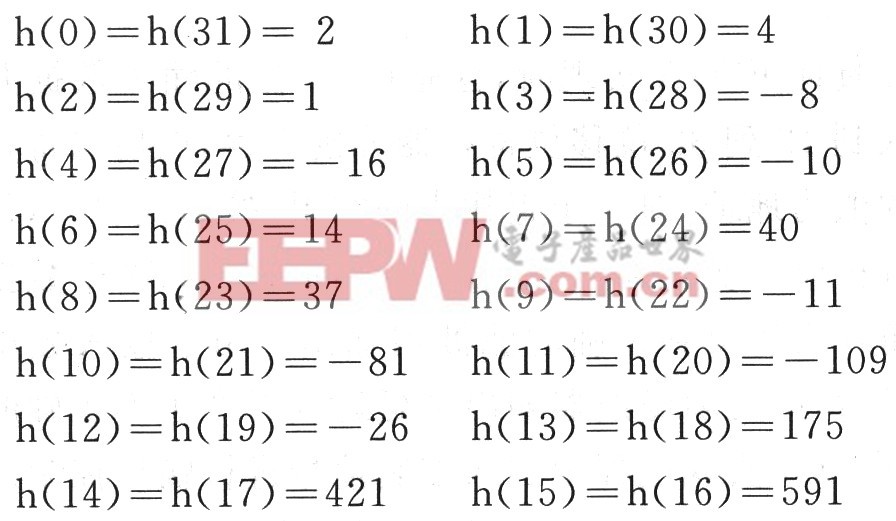

上述求得的系數是浮點型的���,而在FPGA設計中使用的數據是定點型的����,所以在設計濾波器之前要將系數轉化為定點型����,即系數的量化。在本文中采用數字信號處理(DSP)技術中的Q值法對系數進行量化��。為了兼顧精度和所占用的資源�,本文的系數用12位二進制來量化,得到的整數系數結果如下:

評論