基于ARM的嵌入式Linux移植真實(shí)體驗(yàn)(1)――基本概念

ARM是Advanced RISC Machines(高級(jí)精簡(jiǎn)指令系統(tǒng)處理器)的縮寫,是ARM公司提供的一種微處理器知識(shí)產(chǎn)權(quán)(IP)核。

ARM的應(yīng)用已遍及工業(yè)控制、消費(fèi)類電子產(chǎn)品、通信系統(tǒng)、網(wǎng)絡(luò)系統(tǒng)、無(wú)線系統(tǒng)等各類產(chǎn)品市場(chǎng)?;贏RM 技術(shù)的微處理器應(yīng)用約占據(jù)了32位RISC 微處理器75%以上的市場(chǎng)份額。揭開你的手機(jī)、MP3、 PDA,嘿嘿,里面多半藏著一個(gè)基于ARM的微處理器!

ARM內(nèi)核的數(shù)個(gè)系列(ARM7、ARM9、ARM9E、ARM10E、SecurCore、Xscale、StrongARM),各自滿足不同應(yīng)用領(lǐng)域的需求,無(wú)孔不入的滲入嵌入式系統(tǒng)各個(gè)角落的應(yīng)用。這是一個(gè)ARM的時(shí)代!

下面的圖片顯示了ARM的隨處可見:

有人的地方就有江湖(《武林外傳》),有嵌入式系統(tǒng)的地方就有ARM。

構(gòu)建一個(gè)復(fù)雜的嵌入式系統(tǒng),僅有硬件是不夠的,我們還需要進(jìn)行操作系統(tǒng)的移植。我們通常在ARM平臺(tái)上構(gòu)建Windows CE、Linux、Palm OS等操作系統(tǒng),其中Linux具有開放源代碼的優(yōu)點(diǎn)。

下圖顯示了基于ARM嵌入式系統(tǒng)中軟件與硬件的關(guān)系:

日前,筆者作為某嵌入式ARM(硬件)/Linux(軟件)系統(tǒng)的項(xiàng)目負(fù)責(zé)人,帶領(lǐng)項(xiàng)目組成員進(jìn)行了下述工作:

(1)基于ARM920T內(nèi)核S3C2410A CPU的電路板設(shè)計(jì);

(2)ARM處理下底層軟件平臺(tái)搭建:

a.Bootloader的移植;

b.嵌入式Linux操作系統(tǒng)內(nèi)核的移植;

c.嵌入式Linux操作系統(tǒng)根文件系統(tǒng)的創(chuàng)建;

d.電路板上外設(shè)Linux驅(qū)動(dòng)程序的編寫。

本文將真實(shí)地再現(xiàn)本項(xiàng)目開發(fā)過(guò)程中作者的心得,以便與廣大讀者共勉。第一章將簡(jiǎn)單地介紹本ARM開發(fā)板的硬件設(shè)計(jì),第二章分析Bootloader的移植方法,第三章敘述嵌入式 Linux的移植及文件系統(tǒng)的構(gòu)建方法,第四章講解外設(shè)的驅(qū)動(dòng)程序設(shè)計(jì),第五章給出一個(gè)已構(gòu)建好的軟硬件平臺(tái)上應(yīng)用開發(fā)的實(shí)例。

如果您有良好的嵌入式系統(tǒng)開發(fā)基礎(chǔ),您將非常容易領(lǐng)會(huì)本文講解地內(nèi)容。即便是您從來(lái)沒有嵌入式系統(tǒng)的開發(fā)經(jīng)歷,本文也力求讓您讀起來(lái)不覺得生澀。您可以通過(guò)如下email與作者聯(lián)系:21cnbao@21cn.com。

2.ARM體系結(jié)構(gòu)

作為一種RISC體系結(jié)構(gòu)的微處理器,ARM微處理器具有RISC體系結(jié)構(gòu)的典型特征。還具有如下增強(qiáng)特點(diǎn):

(l)在每條數(shù)據(jù)處理指令當(dāng)中,都控制算術(shù)邏輯單元(ALU)和移位器,以使ALU和移位器獲得最大的利用率;

(2)自動(dòng)遞增和自動(dòng)遞減的尋址模式,以優(yōu)化程序中的循環(huán);

(3)同時(shí)Load和Store多條指令,以增加數(shù)據(jù)吞吐量;

(4)所有指令都條件執(zhí)行,以增大執(zhí)行吞吐量。

ARM體系結(jié)構(gòu)的字長(zhǎng)為32位,它們都支持Byte(8位)、Halfword(16位)和Word(32位)3種數(shù)據(jù)類型。

ARM處理器支持7種處理器模式,如下表:

大部分應(yīng)用程序都在User模式下運(yùn)行。當(dāng)處理器處于User模式下時(shí),執(zhí)行的程序無(wú)法訪問(wèn)一些被保護(hù)的系統(tǒng)資源,也不能改變模式,否則就會(huì)導(dǎo)致一次異常。對(duì)系統(tǒng)資源的使用由操作系統(tǒng)來(lái)控制。

User模式之外的其它幾種模式也稱為特權(quán)模式,它們可以完全訪問(wèn)系統(tǒng)資源,可以自由地改變模式。其中的FIQ、IRQ、supervisor、Abort和undefined 5種模式也被稱為異常模式。在處理特定的異常時(shí),系統(tǒng)進(jìn)入這幾種模式。這5種異常模式都有各自的額外的寄存器,用于避免在發(fā)生異常的時(shí)候與用戶模式下的程序發(fā)生沖突。

還有一種模式是system模式,任何異常都不會(huì)導(dǎo)致進(jìn)入這一模式,而且它使用的寄存器和User模式下基本相同。它是一種特權(quán)模式,用于有訪問(wèn)系統(tǒng)資源請(qǐng)求而又需要避免使用額外的寄存器的操作系統(tǒng)任務(wù)。

程序員可見的ARM寄存器共有37個(gè):31個(gè)通用寄存器以及6個(gè)針對(duì)ARM處理器的不同工作模式所設(shè)立的專用狀態(tài)寄存器,如下圖:

ARM9采用5級(jí)流水線操作:指令預(yù)取、譯碼、執(zhí)行、數(shù)據(jù)緩沖、寫回。ARM9設(shè)置了16個(gè)字的數(shù)據(jù)緩沖和4個(gè)字的地址緩沖。這5級(jí)流水已被很多的RISC處理器所采用,被看作RISC結(jié)構(gòu)的“經(jīng)典”。

3.硬件設(shè)計(jì)

3.1 S3C2410A微控制器

電路板上的ARM微控制器S3C2410A采用了ARM920T核,它由ARM9TDMI、存儲(chǔ)管理單元MMU和高速緩存三部分組成。其中,MMU可以管理虛擬內(nèi)存,高速緩存由獨(dú)立的16KB地址和16KB數(shù)據(jù)高速Cache組成。ARM920T有兩個(gè)內(nèi)部協(xié)處理器:CP14和CP15。CP14用于調(diào)試控制,CP15用于存儲(chǔ)系統(tǒng)控制以及測(cè)試控制。

S3C2410A集成了大量的內(nèi)部電路和外圍接口:

Ø LCD控制器(支持STN和TFT帶有觸摸屏的液晶顯示屏)

Ø SDRAM控制器

Ø 3個(gè)通道的UART

Ø 4個(gè)通道的DMA

Ø 4個(gè)具有PWM功能的計(jì)時(shí)器和一個(gè)內(nèi)部時(shí)鐘

Ø 8通道的10位ADC

Ø 觸摸屏接口

Ø I2C總線接口

Ø 12S總線接口

Ø 兩個(gè)USB主機(jī)接口

Ø 一個(gè)USB設(shè)備接口

Ø 兩個(gè)SPI接口

Ø SD接口

Ø MMC卡接口

S3C2410A集成了一個(gè)具有日歷功能的RTC和具有PLL(MPLL和UPLL)的芯片時(shí)鐘發(fā)生器。MPLL產(chǎn)生主時(shí)鐘,能夠使處理器工作頻率最高達(dá)到203MHz。這個(gè)工作頻率能夠使處理器輕松運(yùn)行WinCE、Linux等操作系統(tǒng)以及進(jìn)行較為復(fù)雜的信息處理。UPLL則產(chǎn)生實(shí)現(xiàn)USB模塊的時(shí)鐘。

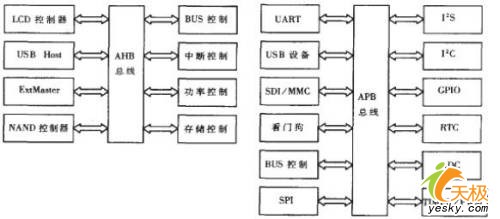

下圖顯示了S3C2410A的集成資源和外圍接口:

我們需要對(duì)上圖中的AHB總線和APB總線的概念進(jìn)行一番解釋。ARM核開發(fā)的目的,是使其作為復(fù)雜片上系統(tǒng)的一個(gè)處理單元來(lái)應(yīng)用的,所以還必須提供一個(gè)ARM與其它片上宏單元通信的接口。為了減少不必要的設(shè)計(jì)資源的浪費(fèi),ARM公司定義了AMBA(Advanced Microcontroller Bus Architecture)總線規(guī)范,它是一組針對(duì)基于ARM核的、片上系統(tǒng)之間通信而設(shè)計(jì)的、標(biāo)準(zhǔn)的、開放協(xié)議。

在AMBA總線規(guī)范中,定義了3種總線:

(l)AHB—Advanced High Performace Bus,用于高性能系統(tǒng)模塊的連接,支持突發(fā)模式數(shù)據(jù)傳輸和事務(wù)分割;

(2)ASB—Advanced System Bus,也用于高性能系統(tǒng)模塊的連接,支持突發(fā)模式數(shù)據(jù)傳輸,這是較老的系統(tǒng)總線格式,后來(lái)由AHB總線替代;

(3)APB—Advanced PeriPheral Bus,用于較低性能外設(shè)的簡(jiǎn)單連接,一般是接在AHB或ASB系統(tǒng)總線上的第二級(jí)總線。

典型的AMBA總線系統(tǒng)如下圖:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/69udv233i8pd.jpg" />

S3C2410A將系統(tǒng)的存儲(chǔ)空間分成8個(gè)bank,每個(gè)bank的大小是128M字節(jié),共1G字節(jié)。Bank0到bank5的開始地址是固定的,用于ROM或SRAM。bank6和bank7可用于ROM、SRAM或SDRAM。所有內(nèi)存塊的訪問(wèn)周期都可編程,外部Wait也能擴(kuò)展訪問(wèn)周期。下圖給出了S3C2410A的內(nèi)存組織:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/g5l8t1g2z6tes.jpg" />

下圖給出了S3C2410A的數(shù)據(jù)總線、地址總線和片選電路:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/3849z191nff5s.jpg" />

SDRAM控制信號(hào)、集成USB接口電路:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/5qhw81in5n35s.jpg" />

內(nèi)核與存儲(chǔ)單元供電電路(S3C2410A對(duì)于片內(nèi)的各個(gè)部件采用了獨(dú)立的電源供給,內(nèi)核采用1.8V供電,存儲(chǔ)單元采用3.3V獨(dú)立供電):

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/286a6i39817vs.jpg" />

JTAG標(biāo)準(zhǔn)通過(guò)邊界掃描技術(shù)提供了對(duì)電路板上每一元件的功能、互聯(lián)及相互間影響進(jìn)行測(cè)試的方法,極大地方便了系統(tǒng)電路的調(diào)試。

測(cè)試接入端口TAP的管腳定義如下:

Ø TCK:專用的邏輯測(cè)試時(shí)鐘,時(shí)鐘上升沿按串行方式對(duì)測(cè)試指令、數(shù)據(jù)及控制信號(hào)進(jìn)行移位操作,下降沿用于對(duì)輸出信號(hào)移位操作;

Ø TMS:測(cè)試模式選擇,在TCK上升沿有效的邏輯測(cè)試控制信號(hào);

Ø TDI:測(cè)試數(shù)據(jù)輸入,用于接收測(cè)試數(shù)據(jù)與測(cè)試指令;

Ø TDO:測(cè)試數(shù)據(jù)輸出,用于測(cè)試數(shù)據(jù)的輸出。

S3C2410A調(diào)試用JTAG接口電路:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/4pq5i0220olm.jpg" />

3.2 SDRAM存儲(chǔ)器

SDRAM被用來(lái)存放操作系統(tǒng)(從FLASH解壓縮拷入)以及存放各類動(dòng)態(tài)數(shù)據(jù),采用SAMSUNG公司的K4S561632,它是4Mxl6bitx4bank的同步DRAM,容量為32MB。用2片K4S561632實(shí)現(xiàn)位擴(kuò)展,使數(shù)據(jù)總線寬度達(dá)到32bit,總?cè)萘窟_(dá)到64MB,將其地址空間映射在S3C2410A的bank6。

SDRAM 所有的輸入和輸出都與系統(tǒng)時(shí)鐘CL K上升沿同步,由輸入信號(hào)RA S、CA S、WE組合產(chǎn)生SDRAM 控制命令,其基本的控制命令如下:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/8tnz2jm9zr77.jpg" />

SDRAM 在具體操作之前首先必須通過(guò)MRS命令設(shè)置模式寄存器,以便確定SDRAM 的列地址延遲、突發(fā)類型、突發(fā)長(zhǎng)度等工作模式;再通過(guò)ACT命令激活對(duì)應(yīng)地址的組,同時(shí)輸入行地址;然后通過(guò)RD 或WR 命令輸入列地址,將相應(yīng)數(shù)據(jù)讀出或?qū)懭雽?duì)應(yīng)的地址;操作完成后用PCH 命令或BT 命令中止讀或?qū)懖僮鳌T跊]有操作的時(shí)候,每隔一段時(shí)間必須用ARF命令刷新數(shù)據(jù),防止數(shù)據(jù)丟失。

下圖給出了SDRAM的連接電路:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/1i6eu87v4s10s.jpg" />

3.3 FLASH存儲(chǔ)器

NOR和NAND是現(xiàn)在市場(chǎng)上兩種主要的非易失閃存技術(shù)。

NOR的特點(diǎn)是芯片內(nèi)執(zhí)行(XIP,Execute In Place),即應(yīng)用程序可直接在Flash閃存內(nèi)運(yùn)行,不必把代碼讀到系統(tǒng)RAM中。NOR的傳輸效率很高,在1~4MB的小容量時(shí)具有很高的成本效益,但是很低的寫入和擦除速度大大影響了它的性能。

NAND結(jié)構(gòu)能提供極高的單元密度,可以達(dá)到高存儲(chǔ)密度,并且寫入和擦除的速度也很快。應(yīng)用NAND的困難在于Flash的管理和需要特殊的系統(tǒng)接口,S3C2410A內(nèi)嵌了NAND FLASH控制器。

S3C2410A支持從GCS0上的NOR FLASH啟動(dòng)(16位或32位)或從NAND FLASH啟動(dòng),需要通過(guò)OM0和OM1上電時(shí)的上下拉來(lái)設(shè)置:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/ssk71un6t4l1.jpg" />

在系統(tǒng)中分別采用了一片NOR FLASH(28F640)和NAND FLASH(K9S1208),電路如下圖:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/7ix3rbe188p5s.jpg" />

3.4串口

S3C2410內(nèi)部集成了UART控制器,實(shí)現(xiàn)了并串轉(zhuǎn)換。外部還需提供CMOS/TTL電平與RS232之間的轉(zhuǎn)換:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/skbuv4xq1f4o.jpg" />

3.5以太網(wǎng)

以太網(wǎng)控制芯片采用CIRRUS LOGIC公司生產(chǎn)的CS8900A,其突出特點(diǎn)是使用靈活,其物理層接口、數(shù)據(jù)傳輸模式和工作模式等都能根據(jù)需要而動(dòng)態(tài)調(diào)整,通過(guò)內(nèi)部寄存器的設(shè)置來(lái)適應(yīng)不同的應(yīng)用環(huán)境。它符合IEEE803.3以太網(wǎng)標(biāo)準(zhǔn),帶有傳送、接收低通濾波的10Base-T連接端口,支持10Base2,10Base5和10Base-F的AUI接口,并能自動(dòng)生成報(bào)頭,自動(dòng)進(jìn)行CRC檢驗(yàn),在沖突后自動(dòng)重發(fā)。

CS8900A支持的傳輸模式有I/O和Memory模式。當(dāng)CS8900A有硬件復(fù)位或軟件復(fù)位時(shí),它將默認(rèn)成為8位工作模式。因此,要使CS8900A工作于16位模式,系統(tǒng)必須在訪問(wèn)之前提供給總線高位使能管腳(/SBHE)一個(gè)由高到低、再由低到高變化的電平。

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/2323iwdi4v89s.jpg" />

3.6 USB接口

USB 系統(tǒng)由USB 主機(jī)(USB Host)、USB集線器(USB Hub)和USB設(shè)備(USB Device)組成。USB 和主機(jī)系統(tǒng)的接口稱作主機(jī)控制器(Host Controller),它是由硬件和軟件結(jié)合實(shí)現(xiàn)的。根集線器是綜合于主機(jī)系統(tǒng)內(nèi)部的,用以提供USB的連接點(diǎn)。USB的設(shè)備包括集線器(Hub)和功能器件(Function)。

S3C2410A集成了USB host和USB device,外部連接電路如下圖:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/t9143dw950y6.jpg" />

3.7電源

LDO(Low Dropout)屬于DC/DC變換器中的降壓變換器,它具有低成本、低噪聲、低功耗等突出優(yōu)點(diǎn),另外它所需要的外圍器件也很少,通常只有 1~2 個(gè)旁路電容。

在電路板上我們分別用兩個(gè)LDO來(lái)實(shí)現(xiàn)5V向3.3V(存儲(chǔ)接口電平)和1.8V(ARM內(nèi)核電平)的轉(zhuǎn)換。

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/110hhvh95i1e.jpg" />

up監(jiān)控電路采用MAX708芯片,提供上電、掉電以及降壓情況下的復(fù)位輸出及低電平有效的人工復(fù)位輸出:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/82ptl9b9g07r.jpg" />

3.8其它

SN74LVTH62245A提供總線驅(qū)動(dòng)和緩沖能力:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/7i9pfpcx6et6s.jpg" />

S3C2410A集成LCD液晶顯示器控制電路,外部引出接口:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/8t32s961ih5u.jpg" />

觸摸屏有電阻式、電容式等,其本質(zhì)是一種將手指在屏幕上的觸點(diǎn)位置轉(zhuǎn)化為電信號(hào)的傳感器。手指觸到屏幕,引起觸點(diǎn)位置電阻或電容的變化,再通過(guò)檢測(cè)這一電性變化,從而獲得手指的坐標(biāo)位置。通過(guò)S3C2410A集成的AD功能,完成電信號(hào)向屏幕坐標(biāo)的轉(zhuǎn)化,觸摸屏接口如下:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/e31e03427b9ms.jpg" />

鍵盤則直接利用CPU的可編程I/O口,若連接 mxn鍵盤,則需要m+n個(gè)可編程I/O口,由軟件實(shí)現(xiàn)鍵盤掃描,識(shí)別按鍵:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/lvoqhd8o5n8b.jpg" />

3.9整體架構(gòu)

下圖呈現(xiàn)了ARM處理器及外圍電路的整體設(shè)計(jì)框架:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/t2658jh1iu8n.gif" />

4.小結(jié)

本章講解了基于S3C2410A ARM處理器電路板硬件設(shè)計(jì)的基本組成,為后續(xù)各章提供了總體性的準(zhǔn)備工作。

評(píng)論