Si5324設(shè)計(jì)的精密時(shí)鐘去抖動技術(shù)

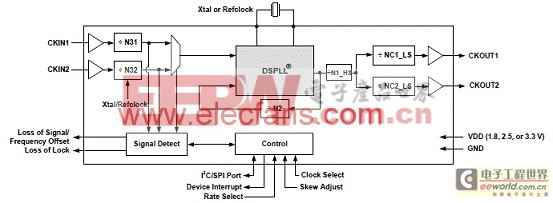

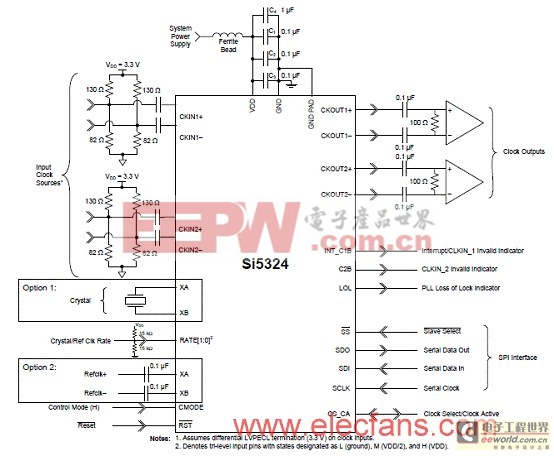

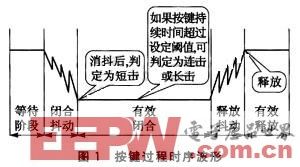

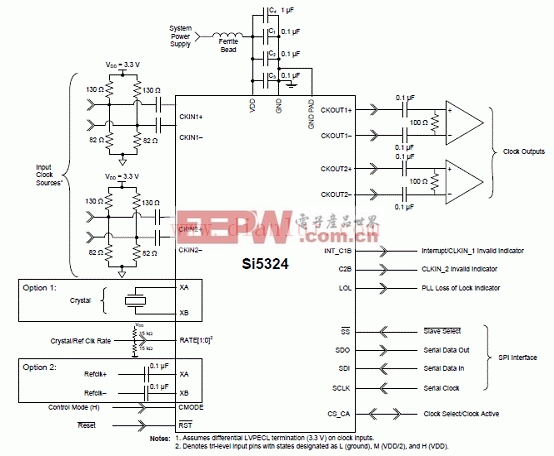

本文介紹了Si5324主要特性,方框圖以及I2C控制模式和SPI 控制模式的典型應(yīng)用電路圖.Silabs 公司的Si5324是精密時(shí)鐘倍頻器/抖動衰減器,用于陡動性能小于1ps的應(yīng)用. Si5324采用兩個(gè)時(shí)鐘輸入,頻率范圍從2 kHz 到 710 MHz,產(chǎn)生兩個(gè)輸出時(shí)鐘,頻率范圍從2 kHz到945 MHz,選擇頻率可到1.4GHz,回路帶寬4– 525 Hz,滿足ITU-T G.8251和 Telcordia GR253-CORE抖動指標(biāo).I2C或SPI編程,單電源1.8 ±5%, 2.5 ±10% 或3.3 V ±10%工作,主要用在廣播視頻如3G/HD/SD-SDI,包光纖傳輸系統(tǒng)(P-OTS), SONET OC-48/192/768, SDH/STM-16/64/256線路卡, GbE/10/40/100G同步以太網(wǎng),數(shù)據(jù)轉(zhuǎn)換,無線基站和測試測量等.

Si5324應(yīng)用:

?

Broadcast video –3G/HD/SD-SDI, Genlock

?

Packet Optical Transport Systems (P-OTS), MSPP

?

OTN OTU-1/2/3/4 Asynchronous Demapping (Gapped Clock)

?

SONET OC-48/192/768, SDH/STM-16/64/256 line cards

?

1/2/4/8/10G Fibre Channel line cards

?

GbE/10/40/100G Synchronous Ethernet (LAN/WAN)

?

Data converter clocking

?

Wireless base stations

?

Test and measurement

圖1.Si5324方框圖

圖2.Si5324典型應(yīng)用電路圖(I2C控制模式)

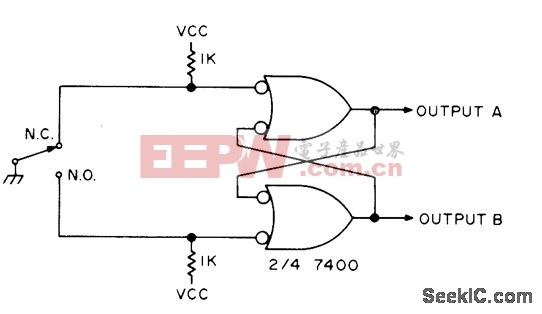

圖3.Si5324典型應(yīng)用電路圖(SPI控制模式)

評論