電源設(shè)計(jì)小貼士 41:DDR內(nèi)存電源

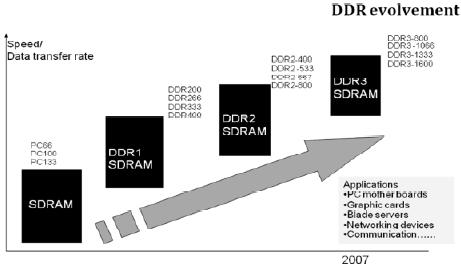

CMOS 邏輯系統(tǒng)的功耗主要與時(shí)鐘頻率、系統(tǒng)內(nèi)各柵極的輸入電容以及電源電壓有關(guān)。器件形體尺寸減小后,電源電壓也隨之降低,從而在柵極層大大降低功耗。這種低電壓器件擁有更低的功耗和更高的運(yùn)行速度,允許系統(tǒng)時(shí)鐘頻率升高至千兆赫茲級(jí)別。在這些高時(shí)鐘頻率下,阻抗控制、正確的總線終止和最小交叉耦合,帶來高保真度的時(shí)鐘信號(hào)。傳統(tǒng)上,邏輯系統(tǒng)僅對(duì)一個(gè)時(shí)鐘沿的數(shù)據(jù)計(jì)時(shí),而雙倍數(shù)據(jù)速率 (DDR) 內(nèi)存同時(shí)對(duì)時(shí)鐘的前沿和下降沿計(jì)時(shí)。它使數(shù)據(jù)通過速度翻了一倍,且系統(tǒng)功耗增加極少。

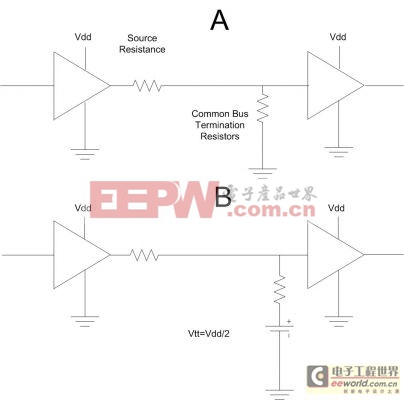

高數(shù)據(jù)速率要求時(shí)鐘分配網(wǎng)絡(luò)設(shè)計(jì)要倍加小心,以此來最小化振鈴和反射效應(yīng),否則可能會(huì)導(dǎo)致對(duì)邏輯器件非有意計(jì)時(shí)。圖 1 顯示了兩種備選總線終止方案。第一種方案(A)中,總線終止電阻器放置于分配網(wǎng)絡(luò)的末端,并連接至接地。如果總線驅(qū)動(dòng)器處于低態(tài)下,電阻器的功耗便為零。在高態(tài)下時(shí),電阻器功耗等于電源電壓(VDD)平方除以總線電阻(源阻抗加端接電阻)。平均功耗為電源電壓平方除以兩倍總線電阻。

圖 1 VTT 端接電壓降低一半端接功耗

第二種方案(B)中,端接電阻器連接至電源電壓 (VTT),電源電壓為 VDD 電壓的一半。電阻器功耗恒定,且與電源電壓無關(guān),其等于 VTT(或(Vdd/2))平方除以端接電阻。相比第一種方法,這種方法產(chǎn)生的功耗僅為其 1/2,但需要增加一個(gè)電源。同時(shí),它對(duì)電源的要求有些特別。首先,其輸出需要為驅(qū)動(dòng)器電壓 (VDD)的一半;其次,它需要同時(shí)輸出電流和汲取電流。當(dāng)驅(qū)動(dòng)器輸出電壓為低時(shí),電流來自 VTT 電源。然而,當(dāng)驅(qū)動(dòng)器為高電平時(shí),電流流入電源。最后,電源還需要在系統(tǒng)數(shù)據(jù)變化時(shí)在各模式之間轉(zhuǎn)換,且必須提供低源阻抗,直到接近系統(tǒng)的時(shí)鐘速率。

根據(jù)端接電阻、時(shí)鐘頻率和系統(tǒng)電容,確定峰值功耗相對(duì)容易。估算平均功耗要更困難一點(diǎn),它可以比 1/10 峰值功耗低好幾倍。由于系統(tǒng)為動(dòng)態(tài)且沒有真正固定不變的時(shí)鐘率,并非每個(gè)周期都對(duì)數(shù)據(jù)計(jì)時(shí),而且會(huì)有一些三態(tài)的器件,因此您需要考慮所有這些因素。

平均電流是驗(yàn)證系統(tǒng)測(cè)量的一個(gè)重要數(shù)值,因?yàn)樗鼘?duì)確定正確的電源拓?fù)浜苤匾?。例如,您可能?huì)在開關(guān)式電源低功耗和線性穩(wěn)壓器的低成本和小體積之間進(jìn)行權(quán)衡。表 1 顯示了開關(guān)式電源和線性穩(wěn)壓器在組件數(shù)目、面積要求、功耗和成本等方面的對(duì)比情況。該表適用于可輸出 3 安峰值電流的一些穩(wěn)壓器。有趣的是,如果峰值電流一直存在的話,就很難處理高功耗。建立 DC 電流將有助于做出正確的選擇。很明顯,從各個(gè)方面來看,線性穩(wěn)壓器都是更佳的選擇。

表 1 線性方法體積更小、成本更低但不如開關(guān)式電源高效。

參數(shù) | 線性 | 開關(guān) |

組件數(shù)目 | 4 | 16 |

電路面積(平方英寸) | ? | 1 |

效率(0.25 A) | 50 % | 88 % |

效率(3A) | 50 % | 90 % |

功耗(0.25 A) | 0.2 W | 0.02 W |

功耗(3A) | 2.3 W | 0.25 |

環(huán)路帶寬 | 1 MHz | 50 kHz |

成本 | X | 2 X |

DDR 電源面臨的一個(gè)巨大挑戰(zhàn)是在高瞬態(tài)負(fù)載極端情況下如何控制輸出電壓。如表 1 所示,線性方法擁有比開關(guān)方法更寬的控制帶寬。因此,它使用更小的電容器來控制輸出阻抗。例如,3 安負(fù)載下要將輸出控制在40mV 以內(nèi),交叉頻率的輸出阻抗需要小于 0.013 Ohms,相當(dāng)于約 10 uF 電容。50 kHz 下線性控制環(huán)路關(guān)閉的開關(guān)式電源使用 200 uF 的電容,從而帶來更多的成本和電路板面積(參閱《電源設(shè)計(jì)小貼士 #10》)

總之,DDR 內(nèi)存通過同時(shí)對(duì)時(shí)鐘兩個(gè)沿的數(shù)據(jù)計(jì)時(shí)提高了系統(tǒng)速度,帶來更高的數(shù)據(jù)傳輸速度。由于是高頻運(yùn)行,要求使用端接電阻器來降低電壓反射。通過將一端同一半電源電壓的電壓連接,可以最小化端接的損耗。這種電源需要能夠輸出或者汲取電流,同時(shí)還必須具有高交叉頻率,來最小化電容器要求。如果升高的功耗在可接受范圍以內(nèi),則端接電源的線性穩(wěn)壓器方法可以節(jié)省成本和減小體積。

評(píng)論