ADSP-TS201的系統(tǒng)設(shè)計(jì)及外部總線接口的技術(shù)

1 引言

本文引用地址:http://www.butianyuan.cn/article/257245.htm 隨著雷達(dá)技術(shù)發(fā)展,大帶寬高分辨力、多種信號(hào)處理方式的采用,使得實(shí)時(shí)信號(hào)處理對(duì)數(shù)據(jù)的處理速度大大提高。同時(shí)在雷達(dá)信號(hào)處理中運(yùn)算量大,數(shù)據(jù)吞吐量急劇上升,對(duì)數(shù)據(jù)處理的要求不斷提高。隨著大規(guī)模集成電路技術(shù)的發(fā)展,作為數(shù)字信號(hào)處理的核心數(shù)字信號(hào)處理器(DSP)得到了快速的發(fā)展和應(yīng)用。ADSP-TS201DSP是美國模擬器件(ADD公司繼TSl01之后推出的一款高性能處理器。此系列DSP性價(jià)比很高,兼有FPGA和ASIC信號(hào)處理性能和指令集處理器的高度可編程性,適用于大存儲(chǔ)量、高性能、高速度的信號(hào)處理和圖像處理。如雷達(dá)信號(hào)處理、無線基站、圖像音頻處理等。

2 ADSP-TS201簡介

ADSP-TS201采用超級(jí)哈佛結(jié)構(gòu),靜態(tài)超標(biāo)量操作適合多處理器模式運(yùn)算,可直接構(gòu)成分布式并行系統(tǒng)和共享存儲(chǔ)式系統(tǒng)。其性能如下:

(1)最高工作主頻可達(dá)600 MHz,指令周期為1.67 ns。支持單指令多數(shù)據(jù)(SIMD)操作。

(2)支持IEEE32位、40位浮點(diǎn)數(shù)據(jù)格式和8位、16位、32位和64位定點(diǎn)數(shù)據(jù)格式。

(3)4條128位的數(shù)據(jù)總線與6個(gè)4 Mb的內(nèi)部RAM相連。

(4)32位的地址總線提供4 G的統(tǒng)一尋址空間。

(5)對(duì)與多片處理器的無縫互連提供片上仲裁。

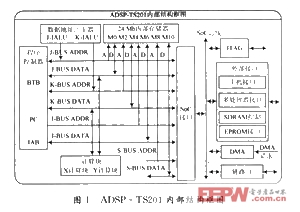

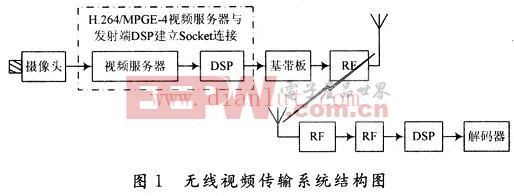

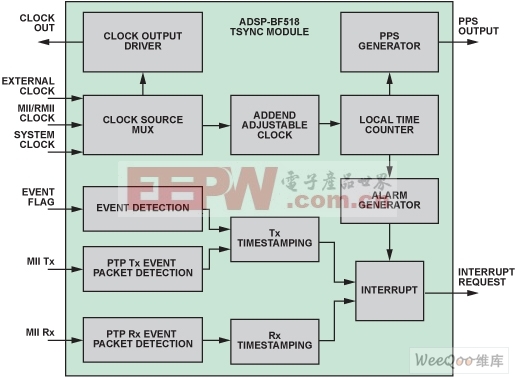

ADSP-TS201處理器由處理器核和IO接口兩部分組成,結(jié)構(gòu)框圖如圖l所示。其中處理器核由兩個(gè)計(jì)算塊、兩個(gè)整型算術(shù)邏輯單元、程序控制器組成。IO接口由內(nèi)部存儲(chǔ)器、外部設(shè)備接口、14通道的DMA控制器、全雙工的LVDS鏈路口、IEEEll49.1JTAG接口組成。內(nèi)部存儲(chǔ)器為24 Mb DRAM,外部設(shè)備接口包括SDRAM控制器、EPROM接口、主機(jī)接口、多處理器接口。

應(yīng)用ADSP-TS201進(jìn)行系統(tǒng)設(shè)計(jì)時(shí),有一些特別需要注意的地方,如:電源設(shè)計(jì)、時(shí)鐘設(shè)計(jì)、JTAG接口、未使用的管腳如何處理等。下面就這幾個(gè)方面分別進(jìn)行討論。

3.1 電源設(shè)計(jì)

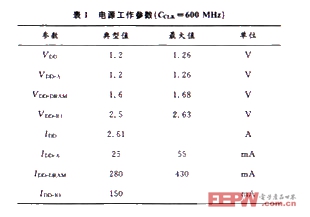

ADSP-TS201處理器共有4組電源,分別是核電源(VDD)、模擬PLL 電源(Vm-1)、內(nèi)部DRAM電源(VDD-DRAM)、IO電源(VDD-K),并且在不同的工作頻率下供電要求不同。以600 MHz為例,電源工作參數(shù)如表1所示。因此設(shè)計(jì)電源的時(shí)候要選擇符合電壓電流要求的電源。

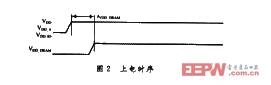

ADSP-TS201在上電的時(shí)候有上電順序的要求,這點(diǎn)在電源設(shè)計(jì)的時(shí)候必須考慮到。其上電順序如圖2所不,要求tVDD_ DRAM大于O ms,保證DRAM的上電在最后,而且上電時(shí)間也要有所保證。所以在選取電源芯片時(shí)應(yīng)該選擇帶有關(guān)斷功能的芯片,如MAX8869等。在電源芯片的SHUTDOWN管腳接一個(gè)電容到地,利用電容的充放電作用,在上電開始使能SHUTDOWN管腳,使電源芯片處于關(guān)斷狀態(tài)。隨著電容充電至電源電壓,SHUTDOWN為高電平,此時(shí)電源芯片開始工作,輸出1.6 V的電壓,為DRAM供電。

另外ADSP-TS201電源管腳需要旁路電容去耦。在PCB設(shè)計(jì)時(shí)旁路電容的順序分別是:VDD A到VSS的旁路電容;VDD到VSS的旁路電容;VDD-DRAM到VSS的旁路電容; VDD-IO到VSS的旁路電容。

3.2 時(shí)鐘設(shè)計(jì)

ADSP-TS201有2個(gè)時(shí)鐘參考電壓管腳,SCLK_VREFl和SCLK_ VREF2,這兩個(gè)管腳應(yīng)該連在一起,為系統(tǒng)時(shí)鐘供電電壓的一半。SCLKl和SCLK2是時(shí)鐘輸入端,最大系統(tǒng)時(shí)鐘是核時(shí)鐘的1/4。同時(shí)SCLK也為外部接口總線提供時(shí)鐘。ADSP一TS201內(nèi)部有一個(gè)PLL,通過設(shè)置SCLKRATE2~0引腳將SCLK倍頻到所需的核時(shí)鐘。在設(shè)計(jì)過程中,為了保證時(shí)鐘的同步,可以采用時(shí)鐘驅(qū)動(dòng)芯片,可以同時(shí)輸出多路時(shí)鐘,為TS201 SDRAM提供系統(tǒng)時(shí)鐘。

3.3 JTAG接口

ADSP-TS201 JTAG仿真器是一個(gè)14腳的母頭,第3腳是沒有任何連接的。在調(diào)試過程中第3腳必須拔出來。在JTAG接口設(shè)計(jì)時(shí)要注意以下方面:正確的上下拉電阻,數(shù)據(jù)(TDI,TMS,TDO,TRST,EMU)驅(qū)動(dòng)、時(shí)鐘驅(qū)動(dòng)如74系列的驅(qū)動(dòng)芯片。

3.4 未使用管腳的處理

ADSP-TS201包含有3個(gè)NC管腳,在設(shè)計(jì)中不要有任何連接。對(duì)于沒有用到的管腳,應(yīng)根據(jù)是單片系統(tǒng)還是多片互連系統(tǒng)進(jìn)行處理,可以懸空的管腳懸空,不能懸空的管腳一定要接上拉電阻或者下拉電阻。特別是沒有用到的鏈路口的輸入管腳的處理,主要參考ADI網(wǎng)站中所給出的數(shù)據(jù)手冊(cè)。

另外TS201支持多片DSP互連,最多可達(dá)8片。通過鏈路口完成片與片之間的通信,電路連接簡單。

4 外部總線接口技術(shù)

ADSP-TS201外部總線支持各種不同的通用/專用協(xié)議,并且可以通過編程進(jìn)行配置。外部總線接口支持流水線協(xié)議,SDRAM協(xié)議和慢速設(shè)備協(xié)議。TS20l可以采用流水線協(xié)議訪問存儲(chǔ)系統(tǒng),數(shù)據(jù)傳送速度非常快。另外TS20l有片上的SDRAM控制器,支持SDRAM協(xié)議。以下就是這兩種協(xié)議的應(yīng)用。

4.1 SDRAM接口

ADSP-TS201處理器有一個(gè)專用的SDRAM接口.可以實(shí)現(xiàn)與標(biāo)準(zhǔn)SDRAM 6 Mb,64 Mb,128 Mb.256 Mb.512 Mb的無縫連接。支持1 024-,512-,256字的頁面長度,通過對(duì)SDRCON寄存器的編程可實(shí)現(xiàn)頁面長度的選擇。同時(shí)SDRAM占用TS201的外部存儲(chǔ)空間地址,通過設(shè)置/MSSD3~0來確定SDRAM的地址空間范圍。

本設(shè)計(jì)選用的SDRAM是HY57V561620B,頁面長度為512字,將兩片SDRAM拼接成32位的總線寬度,實(shí)現(xiàn)與TS201的無縫接口。根據(jù)不同的總線寬度,TS201的地址總線與SDRAM的連接有所不同。

(1)對(duì)于32位數(shù)據(jù)總線其連接方式如下:

SDRAM地址Bit9~0與TS201 ADDR9~0相連;

SD

RAM地址Bitl0與TS201的SDA10管腳相連;

SDRAM地址Bitl5~11與TS201 ADDRl5~11相連。

(2)對(duì)于64位數(shù)據(jù)總線,連接方式如下:

SDRAM地址Bit9~0與TS201 ADDRl0~1相連,TS201 ADDR0懸空;

SDRAM地址Bitl0與TS201的SDAl0管腳相連;

SDRAM地址Bitl4~11與TS201 ADDRl5~12相連。

另外對(duì)于標(biāo)準(zhǔn)的SDRAM(3.3 V),TS201的地址線ADDRl5∽11都可以作為BANK的選擇線。對(duì)于低功率的SDRAM(2.5 V),只有ADDRl5~14可以作為BANK的選擇線。因此在進(jìn)行接VI設(shè)計(jì)時(shí)一定要注意所選擇SDRAM的電參數(shù)。

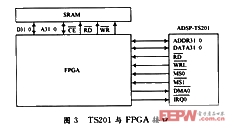

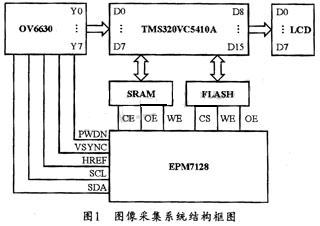

4.2 ADSP-T$201與FPGA接口

本文設(shè)計(jì)的系統(tǒng)需要將FPGA連接在TS201的外部總線上,采用DMA中斷,通過總線的方式從FPGA的外掛RAM(乒乓存儲(chǔ))中讀取數(shù)字下變頻后的I,Q兩路數(shù)據(jù),其連接方式如圖3所示。

其中MS0,MS1是片選信號(hào),RD和WRL分別是讀和寫信號(hào)。在一個(gè)PRF周期內(nèi)FPGA進(jìn)行數(shù)字下變頻,將I,Q數(shù)據(jù)存儲(chǔ)到SRAM中,然后向 TS201發(fā)出DMA請(qǐng)求,TS201將SRAM的數(shù)據(jù)采用流水線協(xié)議通過總線讀入片內(nèi)RAM中,進(jìn)行后續(xù)的處理。再將處理完的數(shù)據(jù)以總線方式寫入到FPGA內(nèi)部RAM中,以便進(jìn)行在線仿真或者進(jìn)行后續(xù)的輸出。

5結(jié) 語

本文主要結(jié)合ADI公司的高性能ADSP-TS201的結(jié)構(gòu)特點(diǎn),討論了在系統(tǒng)設(shè)計(jì)的過程中應(yīng)該重點(diǎn)注意的幾個(gè)問題和ADSP-TS201的外部接口技術(shù),并給出了其與SDRAM,F(xiàn)PGA的連接實(shí)例,對(duì)基于TigerSHARC系列DSP的應(yīng)用設(shè)計(jì)具有實(shí)用的參考價(jià)值。

評(píng)論