采用CAN總線實現(xiàn)DSP芯片程序的受控加載

該技術(shù)使對DSP芯片程序的加載可以脫離仿真器而直接受控于列車的主控機該技術(shù)可靠性高使用靈活方便,具有很強的實用性

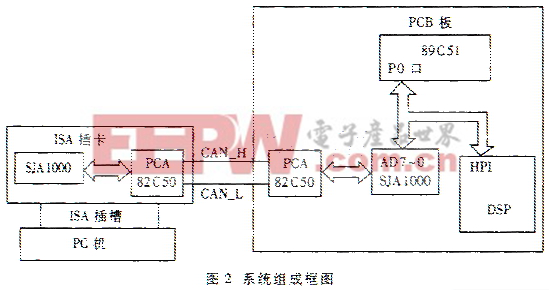

本文引用地址:http://www.butianyuan.cn/article/151307.htm磁懸浮列車上有很多基于DSP芯片的模塊和系統(tǒng)目前, DSP芯片程序的加載與運行都主要依賴于仿真器,而DSP仿真器價格高體積大,這使得磁懸浮列車系統(tǒng)的調(diào)試很不靈活方便;且這些基于DSP芯片的系統(tǒng)一旦脫離仿真器就只能運行事前載入的單一的程序,也使系統(tǒng)的靈活性受到了很大的限制 本文研究了DSP芯片程序加載的基本原理,并根據(jù)這些原理,基于CAN總線,實現(xiàn)了DSP芯片程序的受控加載,使得DSP芯片程序的加載與啟動可直接受控于上位主控機由于主控機的靈活性很大,磁懸浮列車系統(tǒng)在調(diào)試時就可根據(jù)需要對其上各個控制模塊的主控DSP芯片加載不同的程序,控制它的啟動運行,非常方便靈活

CAN Control Area Network,即控制器局域網(wǎng) 總線是一種有效支持分布式控制或定時控制的串行通訊網(wǎng)絡(luò)它以半雙工的方式工作一個節(jié)點發(fā)送信息 多個節(jié)點接收信息 實現(xiàn)了全分布式多機系統(tǒng)提高了數(shù)據(jù)在網(wǎng)絡(luò)中傳輸?shù)目煽啃云浣Y(jié)構(gòu)形式如圖1所示CAN總線的信息存取利用了廣播式的存取工作方式 信息可以在任何時候由任何節(jié)點發(fā)送到空閑的總線上每個節(jié)點的CAN總線接口必須接收總線上出現(xiàn)的所有信息因此各節(jié)點都設(shè)置有一個接收寄存器 該寄存器接收信息 然后根據(jù)信息標(biāo)文符決定是否讀取信息包中的數(shù)據(jù)以判斷是否使用這一信息 CAN總線的特點是以通信數(shù)據(jù)塊編碼代替?zhèn)鹘y(tǒng)的地址編碼 CAN總線面向的是數(shù)據(jù)而不是節(jié)點這種方式的優(yōu)點是可使網(wǎng)絡(luò)內(nèi)的節(jié)點個數(shù)在理論上不受限制 加入或減少設(shè)備不影響整個系統(tǒng)的工作基于CAN總線的各種系統(tǒng)可以根據(jù)用戶需要任意改變節(jié)點數(shù)量CAN總線收發(fā)數(shù)據(jù)的長度最多為8個字節(jié)因而不存在占線時間問題 可以保證通信的實時性通信速率最高可達(dá)1Mb/s距離為40m 最遠(yuǎn)可達(dá)10km速率為5kb/s 對通信介質(zhì)的要求較低可以是光纖或同軸電纜甚至雙絞線

2 DSP芯片的程序加載與運行原理

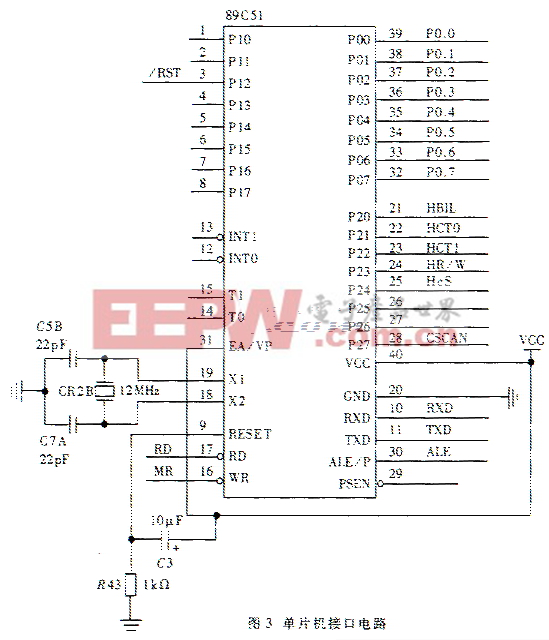

在本項技術(shù)中,DSP的程序加載與啟動運行是通過對其HPI 8位并行口的操作實現(xiàn)的下面先簡單介紹一下DSP的HPI 8位并行口以及如何對它進(jìn)行讀寫操作,然后介紹本文研究的這種DSP程序加載技術(shù)

2.1 DSP芯片的并口(HPI)簡介

HPI并行口的讀寫操作主要由DSP的三個16位寄存器控制,它們分別是:HPIC HPI Control Register,控制寄存器 HPID HPI Data Register,數(shù)據(jù)寄存器 HPIA HPI Adress Register,地址寄存器 寫HPIC寄存器控制HPI并口的讀寫方式以及數(shù)據(jù)高低字節(jié)的讀寫順序等;寫HPIA寄存器控制寫入或讀出數(shù)據(jù)的具體地址(自增模式下2 為數(shù)據(jù)寫入/讀出時的初始地址);從HPID直接寫入/讀出數(shù)據(jù)

HPI有兩種讀寫方式:普通模式下的讀寫按照HPIA的地址將HPID的數(shù)據(jù)寫入內(nèi)存或?qū)⒃摰刂返臄?shù)據(jù)讀入HPID;自增模式下HPIA則是首地址,每次讀或?qū)懖僮骱笏紩詣又赶蛳乱粋€待讀寫的地址

評論