ARM·嵌入式硬件及接口開發(fā)

1.了解開發(fā)板的硬件電路設(shè)計(jì)

2.了解典型的嵌入式系統(tǒng)電路

3.掌握S3C2440下系統(tǒng)時(shí)鐘、GPIN,串口的等工作原理

4.掌握ARM中斷處理機(jī)制

5.掌握S3C2440處理器下中斷處理流程

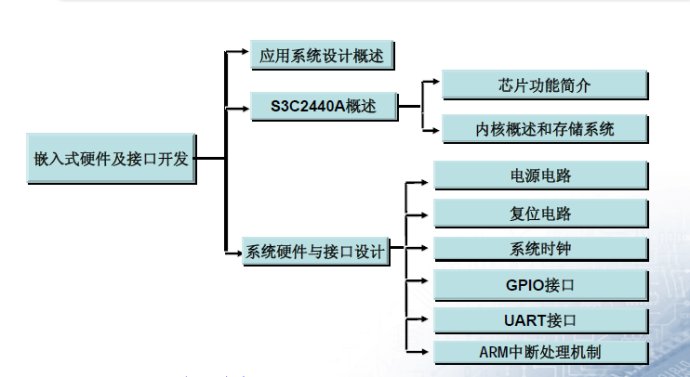

【本章結(jié)構(gòu)】

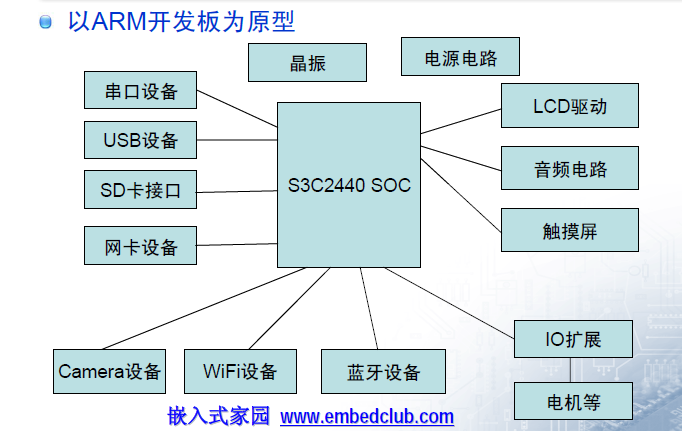

【ARM應(yīng)用系統(tǒng)設(shè)計(jì)的概述】

嵌入式應(yīng)用系統(tǒng)的設(shè)計(jì)需要在硬件和軟件的設(shè)計(jì)之間進(jìn)行權(quán)衡與折中,

硬件實(shí)現(xiàn):執(zhí)行速度高,代碼精簡(jiǎn),但是電路的復(fù)雜度就比較高

軟件實(shí)現(xiàn):可以執(zhí)行復(fù)雜的算法,可以減小硬件設(shè)計(jì)面積和節(jié)約成本,但是軟件復(fù)雜,執(zhí)行速度慢

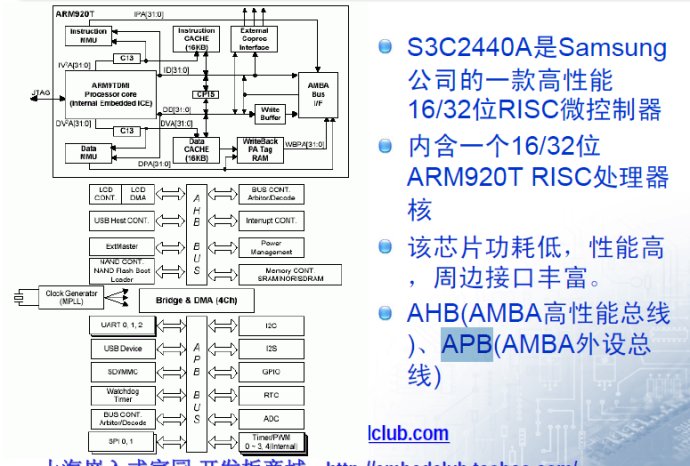

【S3C2440A】

【體系結(jié)構(gòu)】

*用于手持設(shè)備或通用嵌入式應(yīng)用的集成系統(tǒng)

*32位RISC架構(gòu),內(nèi)含效率高,功能強(qiáng)的ARM920T處理器核

*增強(qiáng)ARM架構(gòu)的MMU

*指令cache,數(shù)據(jù)cache,write buffer

*高性價(jià)比、基于JTAG接口的調(diào)試方案

【CPU內(nèi)核】

*支持ARM和Thumb兩種處理器狀態(tài)

*支持大小兩種字節(jié)序

*具有7種操作模式:用戶模式、FIQ快中斷模式、IRQ外部中斷模式、管理模式、異常中止模式、系統(tǒng)模式、未定義模式

*具有37個(gè)寄存器,其中31個(gè)通用寄存器,6個(gè)程序狀態(tài)寄存器

*具有通用的指令構(gòu)造方式

【S3C2440A比較重要的片內(nèi)外圍功能模型包括】

*外部?jī)?nèi)存控制器

*LCD接口

*3個(gè)UART通道/2個(gè)SPI通道

*4個(gè)DMA通道

*1個(gè)I2C通道/1個(gè)I2S通道

*1個(gè)SD卡/MMC卡接口

*2個(gè)USB主機(jī)接口/1個(gè)USB設(shè)備接口

*4個(gè)PWM定時(shí)器和一個(gè)內(nèi)部定時(shí)器

*1個(gè)看門狗定時(shí)器

*130個(gè)可編程I/O口/24個(gè)外部中斷源

*電源控制器,支持Normal,Slow,Idle及Power-off等4種模式

*8通道10bitADC和觸摸屏接口

*帶日歷功能的實(shí)時(shí)時(shí)鐘RTC

*帶PLL的片上時(shí)鐘發(fā)生器

(以后還需要加深理解的)

UART通信,SPI通信,I2C通信

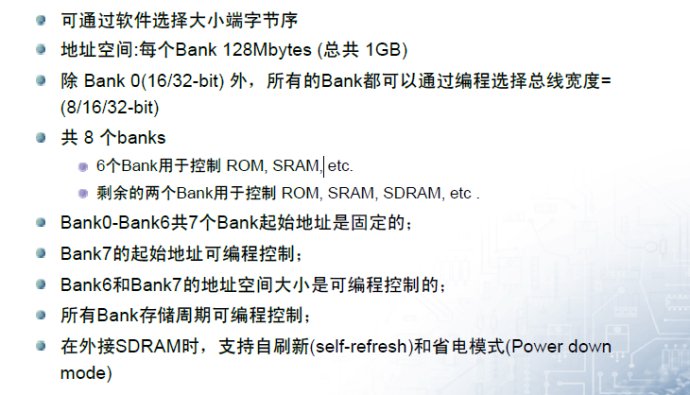

【S3C2440A存儲(chǔ)系統(tǒng)】

0x0000 0000 -0x3FFF FFFF,1GB為外部可尋址空間 ;

0x4800 0000 -0x5FFF FFFF,為處理器內(nèi)部的寄存器地址 ;

剩下的地址空間沒有使用(這也就是為什么理論上尋址空間為4GB,但是訪問不到4GB)

s3c2440A對(duì)外引出

27根地址線:ADDR0-ADDR26

8根片選信號(hào):nGCS0-nGCS7 (每個(gè)片選信號(hào)對(duì)應(yīng)一個(gè)Bankx)

(片選信號(hào)選中時(shí),由bankx控制外設(shè))

【Bank】介紹

評(píng)論