GNU ARM匯編--(六)s3c2440的時鐘控制

PLL Value Selection Guide (MPLLCON)

1. FOUT = 2 * m * Fin / (p*2^S), FVCO = 2 * m * Fin / p where: m=MDIV+8, p=PDIV+2, s=SDIV

2. 600MHz <= FVCO <= 1.2GHz

3. 200MHz <= FCLKOUT <= 600MHz

4. Dont set the P or M value as zero, that is, setting the P=000000, M=00000000 can cause malfunction of

the PLL.

5. The proper range of P and M: 1 <= P <= 62, 1 <= M <= 248

注意:在設(shè)置MPLL和UPLL值的時候,要先設(shè)置UPLL,再設(shè)置MPLL.大約需要內(nèi)部的7個NOP的延時操作.

在datasheet中給出了一個PLL設(shè)置的參考表格.

設(shè)置MPLL的MDIV = 92 PDIV = 1 SDIV = 1

Fout = 2*(92 + 8)*12M/(1+2)/2^1 = 400M

設(shè)置UPLL的MDIV = 56 PDIV = 2 SDIV = 2

Fout = (56+8)*12M/(2+2)/2^2 = 48M

CLOCK CONTROL REGISTER (CLKCON)

這個寄存器控制各個外設(shè)的時鐘時能,是與電源管理相關(guān)的.

CLOCK SLOW CONTROL (CLKSLOW) REGISTER

這個寄存器也是與電源管理相關(guān)的,可以使用默認(rèn)的初始值.

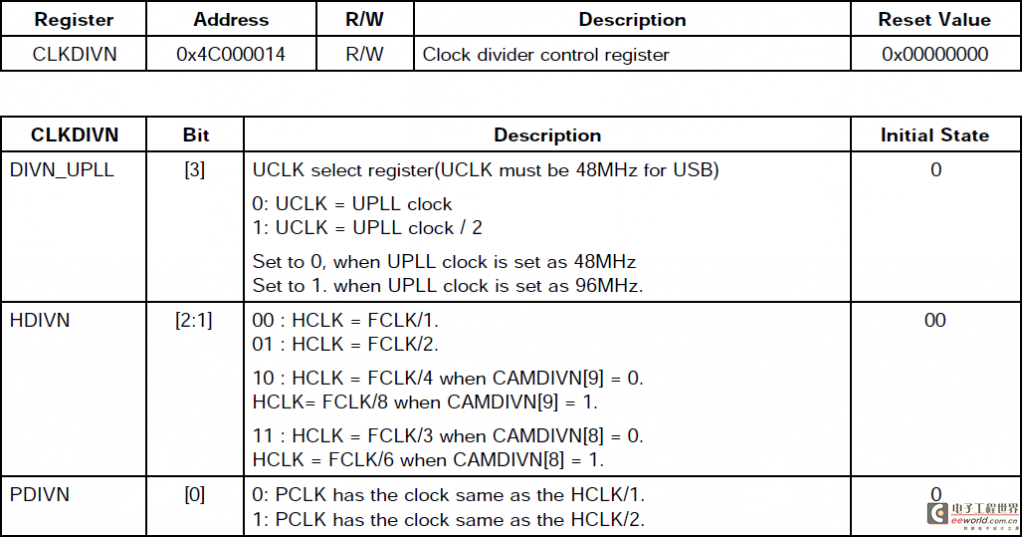

CLOCK DIVIDER CONTROL (CLKDIVN) REGISTER

這個寄存器設(shè)置的是FCLK HCLK PCLK之間的比例:

DIVN_UPLL = 0

UPLL是48M

HDIVN = 01

PDIVN = 1

FCLK : HCLK : PCLK = 1:2:4

datasheet讀懂了,寫出匯編就很容易了,添加了時鐘設(shè)置的流水燈如下:

- .equGPBCON,0x56000010

- .equGPBDAT,0x56000014

- .equGPB5_out,(1<<(5*2))

- .equGPB6_out,(1<<(6*2))

- .equGPB7_out,(1<<(7*2))

- .equGPB8_out,(1<<(8*2))

- .equGPBVALUE,(GPB5_out|GPB6_out|GPB7_out|GPB8_out)

- .equLOCKTIME,0x4c000000

- .equMPLLCON,0x4c000004

- .equUPLLCON,0x4c000008

- .equM_MDIV,92

- .equM_PDIV,1

- .equM_SDIV,1

- .equU_MDIV,56

- .equU_PDIV,2

- .equU_SDIV,2

- .equCLKDIVN,0x4c000014

- .equDIVN_UPLL,0

- .equHDIVN,1

- .equPDIVN,1@FCLK:HCLK:PCLK=1:2:4

- .global_main

- _main:

- ldrr0,=GPBCON

- ldrr1,=0x15400

- strr1,[r0]

- @blclock_setup

- ldrr2,=GPBDAT

- ldrr1,=0x1c0

- strr1,[r2]

- bldelay

- ledloop:

- ldrr1,=0x1c0

- strr1,[r2]

- bldelay

- ldrr1,=0x1a0

- strr1,[r2]

- bldelay

- ldrr1,=0x160

- strr1,[r2]

- bldelay

- ldrr1,=0x0e0

- strr1,[r2]

- bldelay

- bledloop

- clock_setup:

- ldrr0,=LOCKTIME

- ldrr1,=0xffffffff

- strr1,[r0]

- ldrr0,=CLKDIVN

- ldrr1,=(DIVN_UPLL<<3)|(HDIVN<<1)|(PDIVN<<0)

- strr1,[r0]

- ldrr0,=UPLLCON

- ldrr1,=(U_MDIV<<12)|(U_PDIV<<4)|(U_SDIV<<0)@Fin=12MUPLL=48M

- strr1,[r0]

- nop

- nop

- nop

- nop

- nop

- nop

- nop

- ldrr0,=MPLLCON

- ldrr1,=(M_MDIV<<12)|(M_PDIV<<4)|(M_SDIV<<0)@Fin=12MFCLK=400M

- strr1,[r0]

- movpc,lr

- delay:

- @ldrr3,=0xffffffff

- ldrr3,=0xfffff

- delay1:

- subr3,r3,#1

- cmpr3,#0x0

- bnedelay1

- movpc,lr

- 在注釋掉blclock_setup與不注釋的條件對比,流水燈跑的速度明顯不一樣了.在正確設(shè)置時鐘后,后面的各個設(shè)備模塊才可以正確運(yùn)作.

就寫到這里了~~~

評論