HMC741和AD9914的調(diào)試總結(jié)

注意:本文為本人原著,沒有許可不允許轉(zhuǎn)載和抄襲。

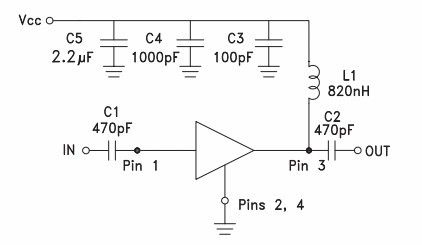

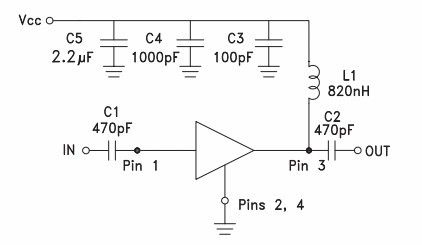

HMC741放大器,其典型電路如下圖:

其決定頻率的關(guān)鍵器件是C1,C2,L1,其中C2的后級電容也起到了隔直的作用,其C1,C2與頻率不匹配的話,就會出現(xiàn)功率衰退厲害,C1如果越小,阻抗電路的頻率越低,在VCC到L1之間可以串聯(lián)電阻進行調(diào)節(jié)放大器功率,此放大器最大功率為20db,VCC推薦電壓是5V,如果到達L1與Fout的電壓低于4.5V,就會把諧波推起來,這是因為放大器工作不正常,因此我們調(diào)節(jié)增益只能適度不是萬能的,這個方法比較危險,因為我們通常都會要求諧波抑制比的。

實際測試中此器件的功率平坦度很好。因此我們?nèi)绻鲆粋€功率很平的頻率,最好是在前級家衰減器進行功率校準,推薦是HMC539,這個衰減器的校準精細度是0.25db,這個這個才是最終調(diào)節(jié)功率的辦法。這里需要注意的是如果L1與C1,C2匹配不好,(通常C1,C2是相等的)那么,容易出現(xiàn)功率跌落的現(xiàn)象,通常臨界點在50—100M附近容易跌落,因此我們需要注意匹配。本人推薦電容為C1=C2=510PF,L1=820NH或則1NH,這個數(shù)值適合在10M—1G的頻率范圍。

AD9914這個器件是目前對大陸禁運的一個器件,好不容易走私回來,現(xiàn)在來分享下,這個器件輸入的參考時鐘達到了3.5G,這個輸入時鐘也就是DDS的工作頻率,輸出頻率最高為1.4G,DDS輸入和輸出有一個比例,通常是40%,輸出等于輸入的百分之四十。這款芯片的雜散相對較高,但是支持的頻率高,支持自動掃頻,并口送數(shù)據(jù),當我們配置完DDS后,切換模式為32bit FTW模式進行刷新FTW,速度超級快,如果是點頻模式的話,700ns可以用FPGA實現(xiàn)100點的跳頻,其實時間最耽誤的是IO updata,更新數(shù)據(jù)有點慢,其他的都很快的。

在調(diào)試中,AD9914的參考頻率輸入在3.2G—3.3G,功率在-3db---5db內(nèi),其雜散最小,雜散我在調(diào)試的時候發(fā)現(xiàn),860---910MHz的時候,雜散最厲害,如果我們處理不好的話,雜散-50多很正常的,因此我們需要注意隔離和濾波等等。我調(diào)試在870M—910M雜散最好的是-62db。參考頻率是PLL出來的3.2G,功率為-4db。在低頻段的時候,雜散非常低,主要是諧波了,在雜散做的最好的DDS應(yīng)該要數(shù)AD9912了,能達到-80多。

在這里面對于調(diào)低9914 的雜散還有一個可怕的做法,就是降低1.8V電壓,降低到1.5-1.6V,雖然雜散好很多,經(jīng)過實際測試,在1.66V 的時候,900M雜散最好,達到-57db,但是電壓過低后,隱患是在上電的時候容易出現(xiàn)不正常,不夠堅挺,容易吧低噪聲推起來。應(yīng)該是器件已經(jīng)掛了。所以不推薦使用。

經(jīng)過實際測試AD9914的1.8V電平是有誤的,他有一個1.8V和3.3V的電壓輸入,但是1.8V實際輸入時候,容易推起很大的雜散,同時,在700M以上,功率如果低于-3db也容易起底噪,因此這些很關(guān)鍵。經(jīng)過實際測試,9914的1.8V電壓實際輸入1.66V時候,雜散是最好的,但是經(jīng)過偶反復(fù)測試,在900MHz和1000MHz,這兩個點的雜散是始終很大的,大約在-55,但是偏移1Hz,就很小了,這個是DDS內(nèi)部的算法造成的,目前解決不掉,除非用開關(guān)濾波組,雜散和頻率的重合點在800M??偨Y(jié):9914傷不起,為什么非要用3.2G的參考,造成使用有小數(shù),雖然是忽略的,就這個造成了雜散,555555555555555.

下面是衰減器HMC424,這個衰減器有個特點,就是如果你都接好了,電路正常,控制腳無虛焊,那么他上電后,輸入端與輸出端對敵都有0.3V的電壓,正負0.1V,過大或則過小都不正常。這個是器件的一個典型特性,也是手冊找不到的,哈哈?。?!

如果描述有錯誤請大家批評指正。

評論