基于FPGA實(shí)現(xiàn)感性元件電阻測試

引言:

本文引用地址:http://butianyuan.cn/article/201701/337463.htm近期給汽車電子某廠商做了一套點(diǎn)火線圈測試系統(tǒng),有一部分是關(guān)于感性線圈電阻測試,具體要求如下:初級(jí)電阻 620 mΩ +-50mΩ、次級(jí)電阻 9.5 kΩ +-0.9 kΩ、導(dǎo)線電阻 150 mΩ +-50 mΩ。

一、挑戰(zhàn):

初級(jí)線圈電阻較?。╩Ω級(jí)),測量過程中還要考慮導(dǎo)線電阻影響;而次級(jí)電阻大(k Ω級(jí)),用DMM數(shù)字萬用表進(jìn)行測試是不錯(cuò)的方案,但是由于測試設(shè)備是放在生產(chǎn)線上,對(duì)體積、功耗和可靠性要求很高,NI CompactRIO平臺(tái)是非常好的選擇,但是NI CompactRIO電阻測試模塊量程大,不適合小電阻測試。并且由于被測件是感性線圈,通過恒電流激勵(lì)4線制測電阻方式,由于恒電流激勵(lì)穩(wěn)定性問題,會(huì) 使得感性線圈產(chǎn)生感應(yīng)電動(dòng)勢,對(duì)小電阻測試帶來考驗(yàn)。

二、方案:

選用NI 9265電流輸出模塊作為電阻測試激勵(lì),通過4線制來測量電壓方式來進(jìn)行電阻測試。為了減小電流激勵(lì)不穩(wěn)定性導(dǎo)致感應(yīng)電動(dòng)勢產(chǎn)生,帶來測量誤差的影響,通過在FPGA用高頻(10k)采樣,然后降采樣到低頻(50-100Hz)模式,濾除感應(yīng)線圈電動(dòng)勢的影響。

三、具體實(shí)施:

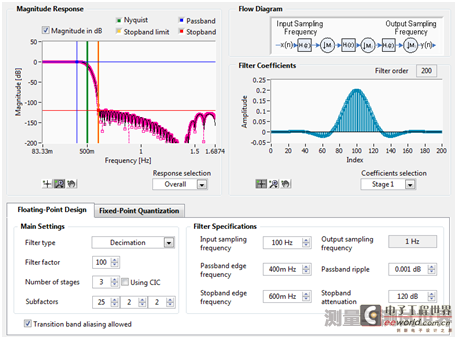

1、 構(gòu)造浮點(diǎn)濾波器:在DFD設(shè)計(jì)工具包選擇Multistage Decimation Filter

圖1、DFD構(gòu)造多級(jí)降采樣浮點(diǎn)濾波器

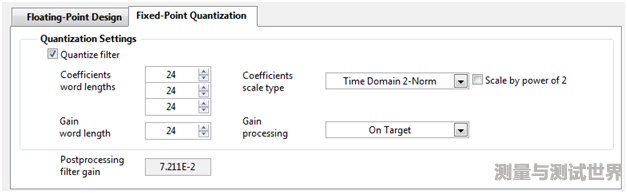

2、 多級(jí)降采樣定點(diǎn)濾波器設(shè)計(jì)

圖2、浮點(diǎn)濾波器量化構(gòu)造定點(diǎn)濾波器

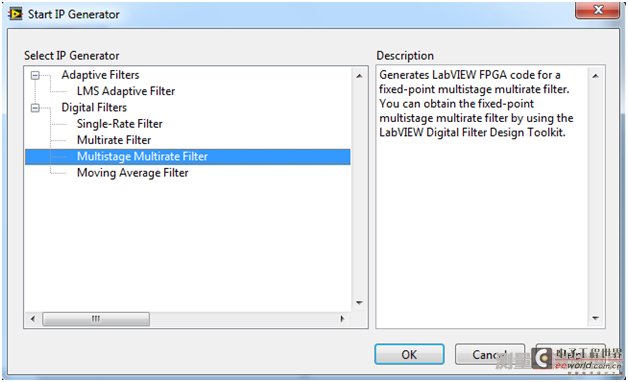

3、 多級(jí)降采樣定點(diǎn)濾波器FPGA實(shí)現(xiàn)

關(guān)鍵詞:

FPGA感性元件電阻測

相關(guān)推薦

技術(shù)專區(qū)

- FPGA

- DSP

- MCU

- 示波器

- 步進(jìn)電機(jī)

- Zigbee

- LabVIEW

- Arduino

- RFID

- NFC

- STM32

- Protel

- GPS

- MSP430

- Multisim

- 濾波器

- CAN總線

- 開關(guān)電源

- 單片機(jī)

- PCB

- USB

- ARM

- CPLD

- 連接器

- MEMS

- CMOS

- MIPS

- EMC

- EDA

- ROM

- 陀螺儀

- VHDL

- 比較器

- Verilog

- 穩(wěn)壓電源

- RAM

- AVR

- 傳感器

- 可控硅

- IGBT

- 嵌入式開發(fā)

- 逆變器

- Quartus

- RS-232

- Cyclone

- 電位器

- 電機(jī)控制

- 藍(lán)牙

- PLC

- PWM

- 汽車電子

- 轉(zhuǎn)換器

- 電源管理

- 信號(hào)放大器

評(píng)論