dds介紹

DDS的簡單介紹

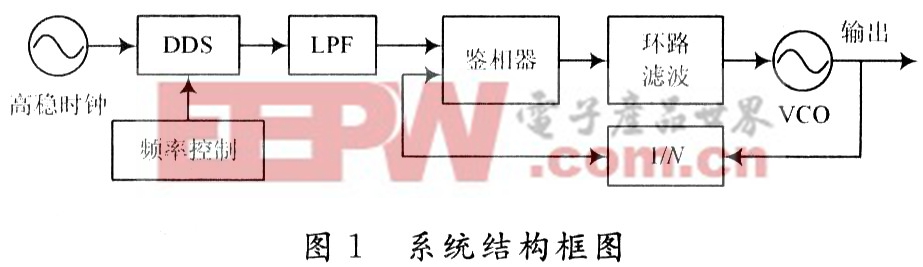

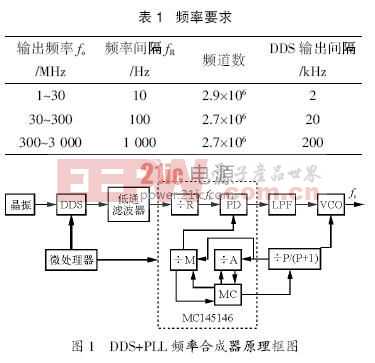

DDS同 DSP(數(shù)字信號處理)一樣,是一項關鍵的數(shù)字化技術(shù)。DDS是直接數(shù)字式頻率合成器(Direct Digital Synthesizer)的英文縮寫。與傳統(tǒng)的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉(zhuǎn)換時間等優(yōu)點,廣泛使用在電信與電子儀器領域,是實現(xiàn)設備全數(shù)字化的一個關鍵技術(shù)。

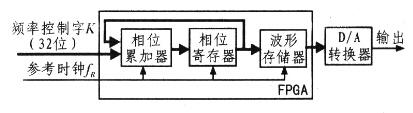

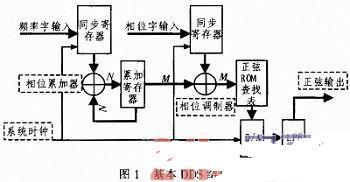

一塊DDS芯片中主要包括頻率控制寄存器、高速相位累加器和正弦計算 [ 查看詳細 ]

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司