3 RS編碼乘法器的Verilog語言描述

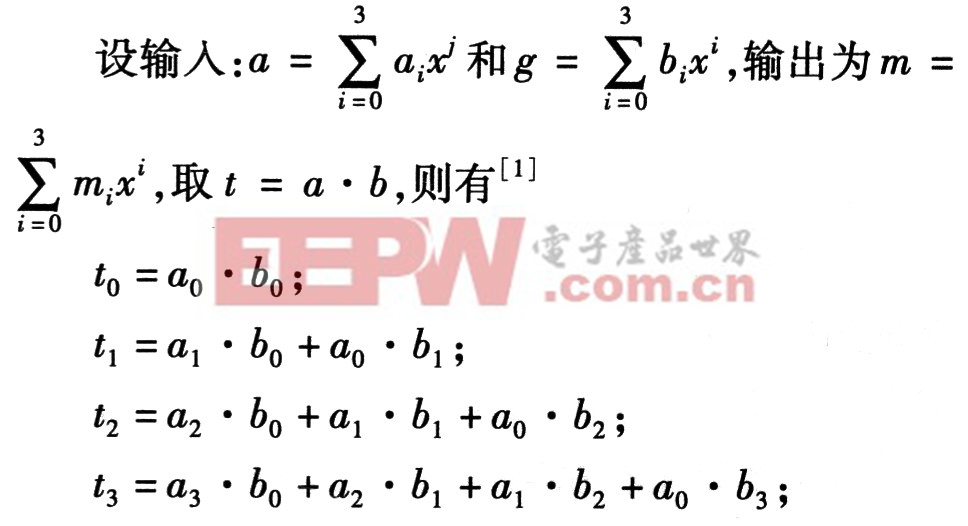

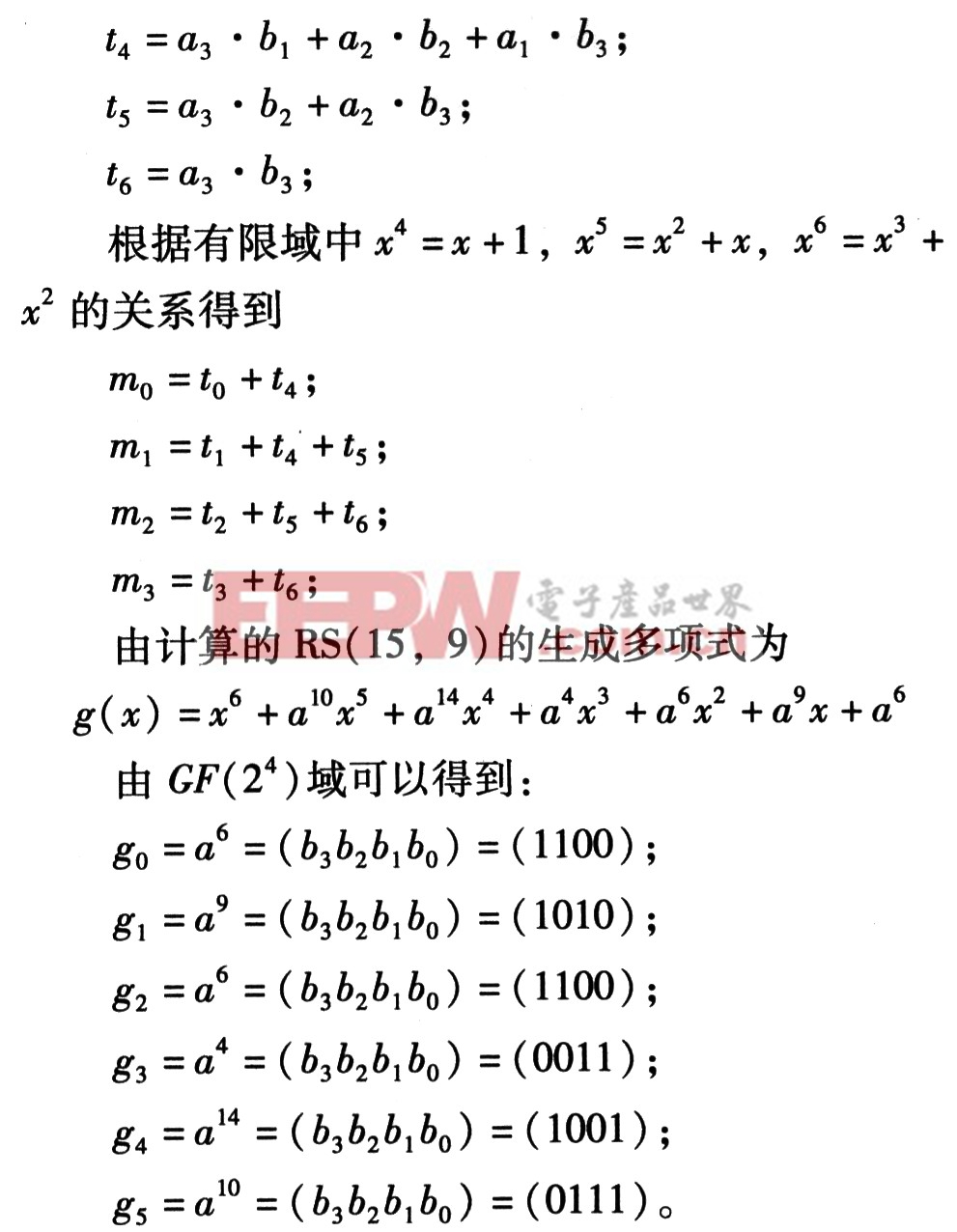

下面以RS(15�����,9)為例描述有限域的乘法實(shí)現(xiàn)思路如下:

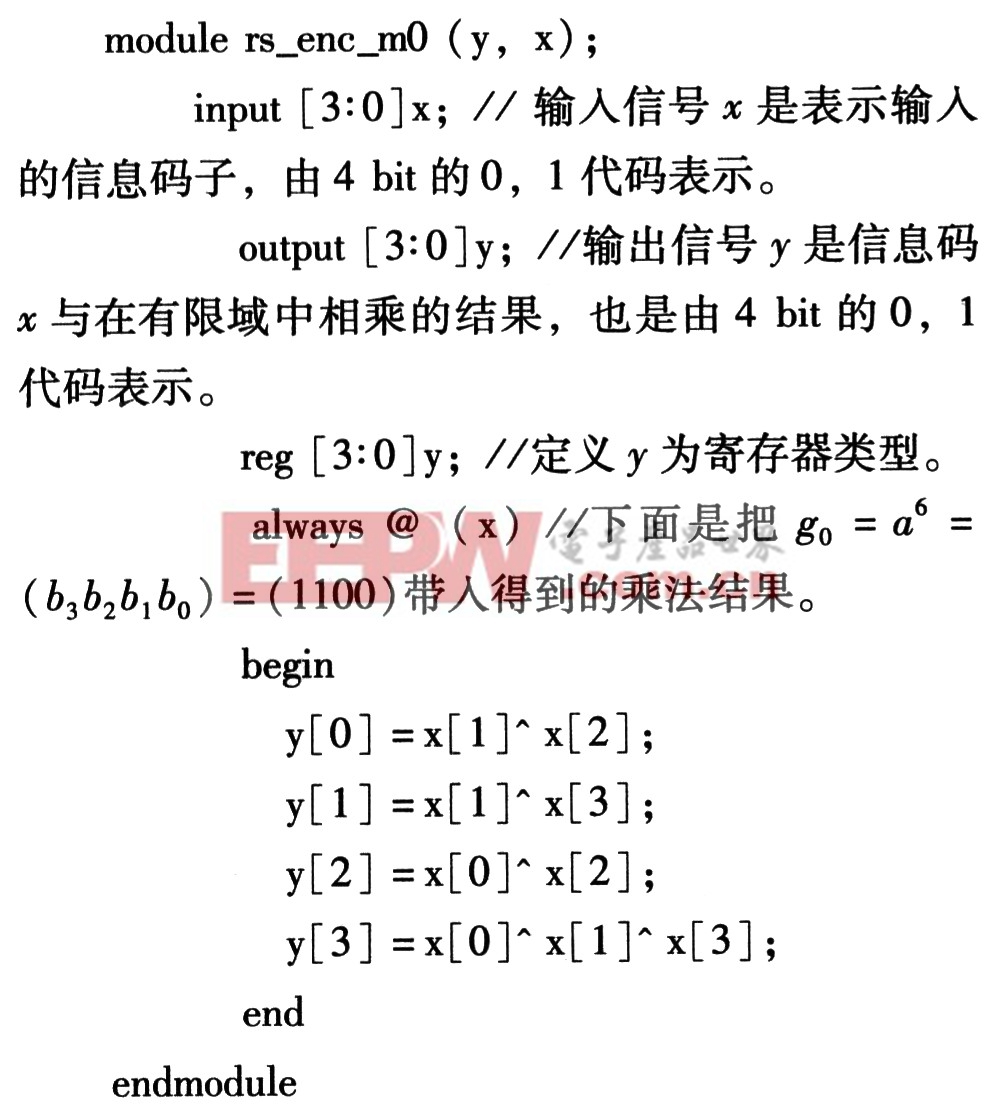

根據(jù)上面的式子可以寫出RS(15,9)的6個(gè)乘法器��。如:與g0相乘的結(jié)果

其余乘法器的描述方法與此類似����。完成對(duì)乘法域的語言描述,剩下的工作就是對(duì)加法器的描述了���,由于加法實(shí)現(xiàn)比較簡單���,這里就不做介紹了。接下來就是控制輸出信息位還是校驗(yàn)位的開關(guān)都是比較好設(shè)計(jì)的����。

評(píng)論